Diferencia entre revisiones de «Semiconductor complementario de óxido metálico»

Deshecha la edición 33603650 de 201.127.65.58 (disc.) |

|||

| Línea 17: | Línea 17: | ||

== Problemas == |

== Problemas == |

||

Hay tres problemas principales relacionados con la tecnología CMOS, aunque no son |

Hay tres problemas principales relacionados con la tecnología CMOS, aunque no son exclusivos de ella: |

||

* '''Sensibilidad a las cargas estáticas'''. Históricamente, este problema se ha resuelto mediante protecciones en las entradas del circuito. Pueden ser diodos en inversa conectados a masa y a la alimentación, que, además de proteger el dispositivo, reducen los [[Régimen transitorio (electrónica)|transitorios]] o [[diodo Zener|zener]] conectados a masa. Este último método permite quitar la alimentación de un sólo dispositivo. |

|||

* '''[[Latch-up]]''': Consiste en la existencia de un [[tiristor]] parásito en la estructura cmos que se dispara cuando la salida supera la alimentación. Esto se produce con relativa facilidad cuando existen [[transitorios]] por usar líneas largas mal adaptadas, excesiva impedancia en la alimentación o alimentación mal desacoplada. El Latch-Up produce un camino de baja resistencia a la corriente de alimentación, de modo que, si no se ha previsto, acarrea la destrucción del dispositivo. Las últimas tecnologías se anuncian como inmunes al latch-up. |

|||

* '''Resistencia a la radiación'''. El comportamiento de la estructura MOS es sumamente sensible a la existencia de cargas atrapadas en el óxido. Una partícula alfa o beta que atraviese un chip CMOS puede dejar cargas a su paso, cambiando la tensión umbral de los transistores y deteriorando o inutilizando el dispositivo. Por ello existen circuitos "endurecidos" (''Hardened''), fabricados habitualmente en silicio sobre aislante (SOI) |

|||

== Enlaces externos == |

== Enlaces externos == |

||

Revisión del 03:18 3 feb 2010

CMOS (del inglés complementary metal-oxide-semiconductor, "estructuras semiconductor-óxido-metal complementarias") es una de las familias lógicas empleadas en la fabricación de circuitos integrados (chips). Su principal característica consiste en la utilización conjunta de transistores de tipo pMOS y tipo nMOS configurados de tal forma que, en estado de reposo, el consumo de energía es únicamente el debido a las corrientes parásitas.

En la actualidad, la mayoría de los circuitos integrados que se fabrican utilizan la tecnología CMOS. Esto incluye microprocesadores, memorias, DSPs y muchos otros tipos de chips digitales.

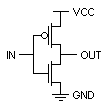

- Cuando la entrada es 1, el transistor nMOS está en estado de conducción. Al estar su fuente conectada a tierra (0), el valor 0 se propaga al drenador y por tanto a la salida de la puerta lógica. El transistor pMOS, por el contrario, está en estado de no conducción

- Cuando la entrada es 0, el transistor pMOS está en estado de conducción. Al estar su fuente conectada a la alimentación (1), el valor 1 se propaga al drenador y por tanto a la salida de la puerta lógica. El transistor nMOS, por el contrario, está en estado de no conducción.

Otra de las características importantes de los circuitos CMOS es que son regenerativos: una señal degradada que acometa una puerta lógica CMOS se verá restaurada a su valor lógico inicial 0 o 1, siempre y cuando aún esté dentro de los márgenes de ruido que el circuito pueda tolerar.

CMOS analógicos

Los

CMOS y Bipolar

Se emplean circuitos mixtos bipolar y CMOS tanto en circuitos analógicos como digitales, en un intento de aprovechar lo mejor de ambas tecnologías. En el ámbito analógico destaca la tecnología BiCMOS, que permite mantener la velocidad y precisión de los circuitos bipolares, pero con la alta impedancia de entrada y márgenes de tensión CMOS. En cuanto a las familias digitales, la idea es cortar las líneas de corriente entre alimentación y masa de un circuito bipolar, colocando transistores MOS. Esto debido a que un transistor bipolar se controla por corriente, mientras que uno MOS, por tensión.

Problemas

Hay tres problemas principales relacionados con la tecnología CMOS, aunque no son exclusivos de ella:

- Sensibilidad a las cargas estáticas. Históricamente, este problema se ha resuelto mediante protecciones en las entradas del circuito. Pueden ser diodos en inversa conectados a masa y a la alimentación, que, además de proteger el dispositivo, reducen los transitorios o zener conectados a masa. Este último método permite quitar la alimentación de un sólo dispositivo.

- Latch-up: Consiste en la existencia de un tiristor parásito en la estructura cmos que se dispara cuando la salida supera la alimentación. Esto se produce con relativa facilidad cuando existen transitorios por usar líneas largas mal adaptadas, excesiva impedancia en la alimentación o alimentación mal desacoplada. El Latch-Up produce un camino de baja resistencia a la corriente de alimentación, de modo que, si no se ha previsto, acarrea la destrucción del dispositivo. Las últimas tecnologías se anuncian como inmunes al latch-up.

- Resistencia a la radiación. El comportamiento de la estructura MOS es sumamente sensible a la existencia de cargas atrapadas en el óxido. Una partícula alfa o beta que atraviese un chip CMOS puede dejar cargas a su paso, cambiando la tensión umbral de los transistores y deteriorando o inutilizando el dispositivo. Por ello existen circuitos "endurecidos" (Hardened), fabricados habitualmente en silicio sobre aislante (SOI)

Enlaces externos

- Puertas NOT y NAND con tecnología CMOS (enlace roto disponible en Internet Archive; véase el historial, la primera versión y la última).