Taxonomía de Flynn

| Una instrucción |

Múltiples instrucciones | |

|---|---|---|

| Un dato |

SISD | MISD |

| Múltiples datos |

SIMD | MIMD |

La taxonomía de Flynn es una clasificación de arquitecturas de computadores, propuesta por Michael J. Flynn en 1966[1] y ampliada en 1972[2]. El sistema de clasificación ha perdurado y se ha utilizado como herramienta en el diseño de procesadores modernos y sus funcionalidades. Desde la aparición de las unidades centrales de multiprocesamiento (CPU), el contexto de la multiprogramación ha evolucionado como una extensión del sistema de clasificación. El procesamiento vectorial, cubierto por la taxonomía de Duncan[3], no aparece en el trabajo de Flynn porque el Cray-1 salió al mercado en 1977: El segundo trabajo de Flynn se publicó en 1972.

Clasificaciones

[editar]Las cuatro clasificaciones definidas por Flynn se basan en el número de instrucciones concurrentes (control) y en los flujos de datos disponibles en la arquitectura:

- Una instrucción, un dato (SISD)

Computador secuencial que no explota el paralelismo en las instrucciones ni en flujos de datos. Es la Arquitectura Von-Neumann. Un único procesador ejecuta un solo flujo de instrucciones para operar datos en una única memoria. Se ejecuta una única instrucción y un dato en cada ciclo de reloj. Puede utilizar técnicas de segmentación o de pipelining. Ejemplos de arquitecturas SISD son las máquinas con uni-procesador o monoprocesador tradicionales como el PC o los antiguos mainframe.

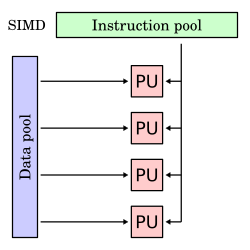

- Una instrucción, múltiples datos (SIMD)

Todas las unidades ejecutan la misma instrucción sincronizadamente, pero con datos distintos. Es un computador que explota varios flujos de datos dentro de un único flujo de instrucciones para realizar operaciones que pueden ser paralelizadas de manera natural. Puede ser de Arquitectura vectorial o Arquitectura matricial.

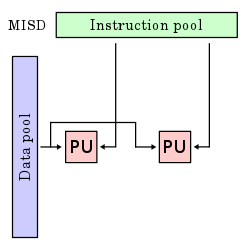

- Múltiples instrucciones, un dato (MISD)

Poco común debido al hecho de que la efectividad de los múltiples flujos de instrucciones suele precisar de múltiples flujos de datos. Sin embargo, este tipo se usa en situaciones de paralelismo redundante, como por ejemplo en navegación aérea, donde se necesitan varios sistemas de respaldo en caso de que uno falle. También se han propuesto algunas arquitecturas teóricas que hacen uso de MISD, pero ninguna llegó a producirse en masa. Algunos autores consideran que las arquitecturas vectoriales supersegmentadas o vectorial escalar forman parte de este modelo ya que en un momento dado se pueden estar manipulando un dato (el vector) por varias instrucciones, no obstante no existe consenso al respecto.

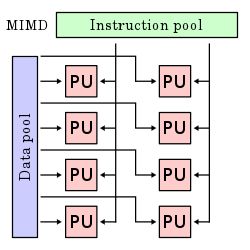

- Múltiples instrucciones, múltiples datos (MIMD)

Varios procesadores autónomos que ejecutan simultáneamente instrucciones diferentes sobre datos diferentes. Los sistemas distribuidos suelen clasificarse como arquitecturas MIMD; bien sea explotando un único espacio compartido de memoria, o uno distribuido.

Diagrama de comparación de las clasificaciones de la Taxonomía de Flynn

[editar]Esas cuatro arquitecturas son mostradas visualmente a continuación en donde cada "PU" (processing unit) es una unidad de procesamiento:

Clasificaciones adicionales

[editar]También existe una extensión común a esta taxonomía que es:

- Un programa, múltiples datos (SPMD) - múltiples procesadores autónomos que trabajan simultáneamente sobre el mismo conjunto de instrucciones (aunque en puntos independientes) sobre datos diferentes. También se le llama 'un proceso, múltiples datos'.

- Múltiples programas, múltiples datos (MPMD) - múltiples procesadores autónomos que trabajan simultáneamente sobre al menos dos programas independientes. Normalmente este sistema elige a un nodo para ser el host o administrador, que corre el programa y otorga los datos a todos los demás nodos que ejecutan un segundo programa. Esos demás nodos devuelven sus resultados directamente al administrador. Un ejemplo podría ser la consola de Sony PlayStation 3, que tiene la arquitectura de procesador SPU/PPU.

Referencias

[editar]- ↑ Flynn, Michael J. (December 1966). «Very high-speed computing systems». Proceedings of the IEEE 54 (12): 1901-1909. doi:10.1109/PROC.1966.5273.

- ↑ Flynn, Michael J. (September 1972). «Some Computer Organizations and Their Effectiveness». IEEE Transactions on Computers. C-21 (9): 948-960. S2CID 18573685. doi:10.1109/TC.1972.5009071.

- ↑ Duncan, Ralph (February 1990). «A Survey of Parallel Computer Architectures». Computer 23 (2): 5-16. S2CID 15036692. doi:10.1109/2.44900. Archivado desde el original el 18 de julio de 2018. Consultado el 18 de julio de 2018.