Diferencia entre revisiones de «Circuito comparador»

m Revertidos los cambios de 201.230.195.213 (disc.) a la última edición de 148.206.74.15 |

|||

| Línea 281: | Línea 281: | ||

== Referencias. == |

== Referencias. == |

||

El método empleado para desarrollar el circuito comparador visto es una extensión del emplea en el libro "Diseño Lógico" de Antonio |

El método empleado para desarrollar el circuito comparador visto es una extensión del emplea en el libro "Diseño Lógico" de Antonio Lloris y Alberto Prieto. |

||

== oliver viera saucedo == |

|||

== Software para realizar los diseños. == |

== Software para realizar los diseños. == |

||

Todos los diagramas se pueden replicar y probar utilizando un simulador y diseñador de circuitos como Ktechlab disponible para la plataforma GNU/Linux. |

Todos los diagramas se pueden replicar y probar utilizando un simulador y diseñador de circuitos como Ktechlab disponible para la plataforma GNU/Linux. |

||

[[Categoría:Circuitos digitales|Comparador, circuito]] |

|||

--[[Especial:Contributions/201.230.195.213|201.230.195.213]] ([[Usuario Discusión:201.230.195.213|discusión]]) 13:17 17 dic 2009 (UTC)[[Media:[['''''==WINDER LA MARAVILLA instituto superior tecnologico almirante miguel grau piura-peru ==''''']]]] |

|||

Revisión del 13:23 17 dic 2009

Un circuito comparador combinatorio compara dos entradas binarias (A y B de n bits) para indicar la relación de igualdad o desigualdad entre ellas por medio de "tres banderas lógicas" que corresponden a las relaciones A igual B, A mayor que B y A menor que B. Cada una de estas banderas se activara solo cuando la relación a la que corresponde sea verdadera, es decir, su salida será 1 y las otras dos producirán una salida igual a cero.

Dentro de la familia de circuitos TTL se les denomina a estos circuitos con el número 7485 y manejan entradas de 4 bits, además de que también se les puede conectar en cascada para manejar entradas más grandes.

Introducción.

Mediante álgebra de Boole y diagramas se quiere mostrar como se puede construir fácilmente un comparador binario de n bits a partir de comparadores más simples de dos y cuatro bits para implementar de manera rápida uno de estos circuitos combinatorios. Todo el texto cubrirá de manera detalla los procesos y análisis requeridos para desarrollar un comparador que puede procesar números enteros con signo y retorne su salida activando con una señal igual a 1 la bandera que indique el tipo de relación entre dos números binarios de n bits.

Metodología.

Para diseñar este circuito se va requerir un conocimiento intermedio del álgebra booleana y la simplificación booleana, uso de tablas de verdad, lógica y diseño de circuitos lógicos, se recomienda también tener un programa para diseñar circuitos lógicos como Ktechlab para crear los diagramas.

Algunas expresiones booleanas se van a representar como funciones cuyo nombre corresponderá a una letra mayúscula del alfabeto para simplificar su representación, mientras que la salida principal en el diagrama de un circuito se va a representar como una función.

Así mismo a las entradas/salidas de n bits que corresponden a un solo dato se les llamara vectores, cada uno de esos vectores será nombrado con un letra mayúscula y cada entrada de un bit dentro de un vector se identificará con el nombre del vector mas la posición que ocupa dentro de él, por ejemplo una entrada de 5 bits se llamaría A y a cada posición dentro del vector A se le llamaría así: A4 que seria el bit más significativo, A3, A2, A1 y A0 que correspondería al bit menos significativo.

Diseño de un circuito comparador de 2 bits.

Para este caso solo se requiere crear la tabla de verdad correspondiente y luego determinar las funciones booleanas que producen las salidas requeridas.

Sean A y B entradas de un bit, entonces:

| A | B | X | Q | Z |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

"X" es la función que determina cuando A < B es verdadero, de modo tal que:

X(A,B) = A‘B

"Q" es la función que determina cuando A = B es verdadero, de modo tal que:

Q(A,B) = A‘B‘ + AB

"Z" es la función que determina cuando A > B es verdadero, de modo tal que:

Z(A,B) = AB‘

Figura.1 Diagrama de un comparador binario de 2 bits.

Diseño de un circuito comparador de n bits.

Antes de construir un comparador binario en cascada se va mostrar como a partir de las expresiones obtenidas en el apartado anterior es posible construir cualquier comparador de n bits utilizando lógica y álgebra booleana. Así se definirá el razonamiento que lleva a la formulación de un caso general para n bits y luego se dará un ejemplo para la expresión requerida para un comparador de 4 bits.

Sean A y B dos vectores de 2 bits. [blanca]

Circuito A=B de n bits.

Aquí es evidente que dos entradas de n bits A y B, son iguales si solo si, son iguales bit a bit, es decir:

A = B si y solo si Q(An-1,Bn-1)*Q(An-2,Bn-2)*...*Q(A1,B1)*Q(A0, B0) = 1

Por lo tanto, si n=4, tenemos que:

A = B si y solo si Q(A3, B3)*Q(A2 B2)*Q(A1,B1)*Q(A0,B0) = 1

En adelante, A=B se denominara como F(A,B)

Circuito A>B de n bits.

Para este caso se va crear una expresión general similar, cuyo enunciado seria:

A > B si y solo si Z(An-1,Bn-1) + Q(An-1,Bn-1)*Z(An-2,Bn-2) + Q(An-1,Bn-1)*Q(An-2,Bn-2)*Z(An-3,Bn-3) +... + Q(An-1,Bn-1)*Q(An-2,Bn-2)*...*Q(A1,B1)*Z(A0,B0) = 1

Por lo tanto, si n=4, tenemos que:

A > B si y solo si Z(A3,B3) + Q(A3,B3)*Z(A2,B2) + Q(A3,B3)*Q(A2,B2)*Z(A1,B1) + Q(A3,B3)*Q(A2,B2)*Q(A1,B1)*Z(A0,B0) = 1

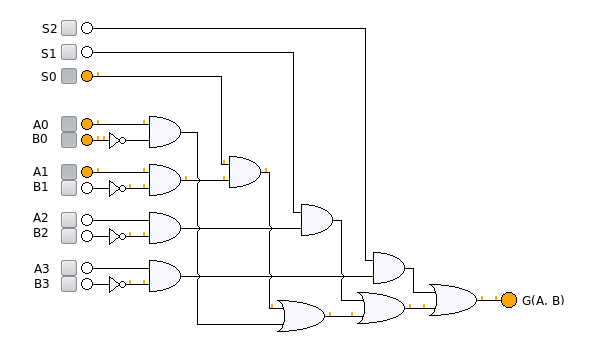

En adelante, A>B se denominara como G(A,B)

Circuito A<B de n bits.

Formalmente este caso define como:

A < B si y solo si X(An-1,Bn-1) + Q(An-1,Bn-1)*X(An-2,Bn-2) + Q(An-1,Bn-1)*Q(An-2,Bn-2)*X(An-3,Bn-3) +... + Q(An-1,Bn-1)*Q(An-2,Bn-2)*...*Q(A1,B1)*X(A0,B0) = 1

Por lo tanto, si n=4, tenemos que:

A < B si y solo si X(A3,B3) + Q(A3,B3)*X(A2,B2) + Q(A3,B3)*Q(A2,B2)*X(A1,B1) + Q(A3,B3)*Q(A2,B2)*Q(A1,B1)*X(A0,B0) = 1

En adelante, A<B se denominara como H(A,B)

Pero por deducción, se puede concluir que: si A=B es FALSO y A>B es FALSO, entonces A<B es VERDADERO lo que seria igual a H(A,B)= [F(A,B)]‘[G(A,B)]‘. Si se implementa la conclusión anterior mediante compuertas lógicas entonces se habría un gran ahorro de trabajo en el diseño y construcción del circuito.

También cabe señalar que la función "Q" puede ser reemplazada por una compuerta NXOR.

Esquemas de los circuitos y reutilización de compuertas.

Al construir el diagrama o esquema del circuito comparador se debe comenzar alambrando la salida de F(A,B) para reducir la cantidad de compuertas que se van a requerir ya que ello permitirá obtener el resultado de las operaciones NXOR necesarias para construir la función G(A,B), también se usara la expresión H(A,B)= [F(A,B)]‘[G(A,B)]‘ para simplificar aún más el diseño.

Figura 2. Mediante compuertas NXOR unidas por más compuertas AND, se obtiene la función F(A,B) a la vez que se usa la salida de cada AND y el primer NXOR para formar un vector de salida adicional que se denominara S de 3 bits de longitud.

Figura 3. Luego utilizando a cada línea del nuevo vector S se construye la función G(A,B), véase "Circuito A>B de n bits." para saber por que.

Diseño de las salidas del comparador binario.

Por ultimo el siguiente diagrama muestra como se juntan las salidas de F(A,B) y G(A,B), A=B y A>B respectivamente, para crear la salida de H(A,B) o mejor dicho A<B, y por fin tener las tres banderas lógicas que indicaran cual es la relación de igualdad o desigualdad entre los vectores de entrada A y B de n bits de largo (que en el caso de este ejemplo seria 4).

Figura 4. Salidas del circuito comparador.

Diseño de un circuito comparador de n bits con signo.

El circuito comparador de n bits con signo que se va a implementar se basa en el circuito comparador que se diseñó antes e incluye varias características adicionales.

- todas las entradas se expresan como enteros binarios en la notación signo-magnitud - el bit de signo corresponde a la posición n-1 (el bit más significativo del vector) - las magnitudes y los signos se procesan por separado

De las anteriores características, la única que se va examinar a fondo es la ultima, ya que en el circuito comparador con signo que se va a implementar compara primero las magnitudes de las entradas, el resultado de esa comparación (en adelante conocido como premisa) junto con el signo de cada entrada permite determinar la salida definitiva de este nuevo circuito.

En total hay tres premisas que se verán a continuación y cada una de ellas produce tres salidas que corresponderán a las banderas A=B, A>B o A<B; cuyo valor será verdadero si y solo si la premisa asociada es verdadera.

Sea J el bit de signo correspondiente a la entrada A, y...

Sea K el bit de signo correspondiente a la entrada B.

Premisa 1.

El resultado de la función F(A,B) = 1; o sea A es igual que B

Si la premisa 1 es cierta, entonces la siguiente tabla de verdad también es cierta:

| J | K | A=B | A>B | A<B |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | 0 |

De manera tal que:

A=B es igual a NXOR(J,K) * F(A,B)

A>B es igual a J‘K * F(A,B)

A<B es igual a JK‘ * F(A,B)

Premisa 2.

El resultado de la función G(A,B) = 1; o sea A es mayor que B

Si la premisa 2 es cierta, entonces la siguiente tabla de verdad también es cierta:

| J | K | A=B | A>B | A<B |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

A=B es 0; por lo tanto no se toma en cuenta.

A>B es igual a J‘*G(A,B)

A<B es igual a J*G(A,B)

Premisa 3.

El resultado de la función H(A,B) = 1; o sea A es menor que B

Si la premisa 2 es cierta, entonces la siguiente tabla de verdad también es cierta:

| J | K | A=B | A>B | A<B |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

A=B es 0; por lo tanto no se toma en cuenta.

A>B es igual a K*H(A,B)

A<B es igual a K‘*H(A,B)

Diseño de las salidas del comparador binario con signo.

En el siguiente diagrama se muestra como se integran las premisas 1,2 y 3 que en total generan 7 salidas para obtener solo 3 que indicaran cual es la relación entre las entradas A y B de n bits con signo, sabiendo que solo hay una premisa cierta y que las otras son falsas.

Consideraciones.

Se debe señalar que un modo de refinar los diagramas mostrados sería usar buffers para compensar la velocidad de cada bit de salida; por ejemplo en la figura 2 se puede apreciar que para generar el vector de salida S cada bit pasa por una cantidad distinta de compuertas, al respecto de puede decir que el tiempo que requiere el vector S para producir su salida es igual al tiempo que tarda en salir bit que requiere de más compuertas para para dar su valor correcto, el bit más lento por decirlo de otra forma; sin embargo el uso de los buffers y el calculo de los tiempos de un circuito están más allá del ámbito que cubre esta página.

Referencias.

El método empleado para desarrollar el circuito comparador visto es una extensión del emplea en el libro "Diseño Lógico" de Antonio Lloris y Alberto Prieto.

Software para realizar los diseños.

Todos los diagramas se pueden replicar y probar utilizando un simulador y diseñador de circuitos como Ktechlab disponible para la plataforma GNU/Linux.