Semiconductor complementario de óxido metálico

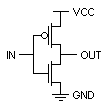

El semiconductor complementario de óxido metálico o complementary metal-oxide-semiconductor (CMOS) es una de las familias lógicas empleadas en la fabricación de circuitos integrados. Su principal característica consiste en la utilización conjunta de transistores de tipo pMOS y tipo nMOS configurados de forma tal que, en estado de reposo, el consumo de energía es únicamente el debido a las corrientes parásitas, colocado en la placa base.

En la actualidad, la mayoría de los circuitos integrados que se fabrican usan la tecnología CMOS. Esto incluye microprocesadores, memorias, procesadores digitales de señales, sensores y muchos otros tipos de circuitos integrados digitales de consumo considerablemente bajo.

Drenador (D) conectada a tierra (Vss), con valor 0; el valor 0 no se propaga al surtidor (S) y por lo tanto a la salida de la puerta lógica. El transistor pMOS, por el contrario, está en estado de conducción y es el que propaga valor 1 (Vdd) a la salida.

Otra característica importante de los circuitos CMOS es que son “regenerativos”: una señal degradada que acometa una puerta lógica CMOS se verá restaurada a su valor lógico inicial 0 o 1, siempre que aún esté dentro de los márgenes de ruido que el circuito pueda tolerar.[1]

Historia

[editar]La tecnología CMOS fue desarrollada por Wanlass y Sah,[2] de Fairchild Semiconductor, a principios de los años 1960. Sin embargo, su introducción comercial se debe a RCA, con su famosa familia lógica CD4000.

Posteriormente, la introducción de un búfer y mejoras en el proceso de oxidación local condujeron a la introducción de la serie 4000B, de gran éxito debido a su bajo consumo (prácticamente cero, en condiciones estáticas) y gran margen de alimentación (de 3 a 18 V).

RCA también fabricó LSI en esta tecnología, como su familia COSMAC de amplia aceptación en determinados sectores, a pesar de ser un producto caro, debido a la mayor dificultad de fabricación frente a dispositivos NMOS.

Pero su talón de Aquiles consistía en su reducida velocidad. Cuando se aumenta la frecuencia de reloj, su consumo sube proporcionalmente, haciéndose mayor que el de otras tecnologías. Esto se debe a dos factores:

- La capacidad MOS, intrínseca a los transistores MOS.

- La utilización de MOS de canal P, más lentos que los de canal N, por ser la movilidad de los huecos menor que la de los electrones.

El otro factor negativo era la complejidad que conlleva el fabricar los dos tipos de transistores, que obliga a utilizar un mayor número de máscaras.

Por estos motivos, a comienzos de los 80, algunos autores pronosticaban el final de la tecnología CMOS, que sería sustituida por la novedosa I2L, entonces prometedora.

Esta fue la situación durante una década, para, en los ochenta, cambia el escenario rápidamente:

- Por un lado, las mejoras en los materiales, técnicas de litografía y fabricación, permitían reducir el tamaño de los transistores, con lo que la capacidad MOS resultaba cada vez menor.

- Por otro, la integración de dispositivos cada vez más complejos obligaba a la introducción de un mayor número de máscaras para asegurar el aislamiento entre transistores, de modo que no era más difícil la fabricación de CMOS que de NMOS.

En este momento empezó una eclosión de memorias CMOS, pasando de 256x4 bits de la 5101 a 2kx8 de la 6116 y 8Kx8 en la 6264, superando, tanto en capacidad como consumo reducido y velocidad a sus contrapartidas NMOS. También los microprocesadores, NMOS hasta la fecha, comenzaron a aparecer en versiones CMOS (80C85, 80C88, 65C02, etc.).

Y aparecieron nuevas familias lógicas, HC y HCT en competencia directa con la TTL-LS, dominadora del sector digital hasta el momento.

Para entender la velocidad de estos nuevos CMOS, hay que considerar la arquitectura de los circuitos NMOS:

- Uso de cargas activas. Esto es, un transistor se polariza con otros transistores y no con resistencias debido al menor tamaño de aquellos. Además, el transistor MOS funciona fácilmente como fuente de corriente constante. Entonces un inversor se hace conectando el transistor inversor a la carga activa. Cuando se satura el transistor, drena toda la corriente de la carga y el nivel da salida baja. Cuando se corta, la carga activa inyecta corriente hasta que el nivel de salida sube. Y aquí está el compromiso: es deseable una corriente pequeña porque reduce la necesidad de superficie en el silicio (transistores más pequeños) y la disipación (menor consumo). Pero las transiciones de nivel bajo a nivel alto se realizan porque la carga activa carga la capacidad MOS del siguiente transistor, además de las capacidades parásitas que existan, por lo que una corriente elevada es mejor, pues se cargan las capacidades rápidamente.

- Estructuras de almacenamiento dinámicas. La propia capacidad MOS se puede utilizar para retener la información durante cortos periodos de tiempo. Este medio ahorra transistores frente al biestable estático. Como la capacidad MOS es relativamente pequeña, en esta aplicación hay que usar transistores grandes y corrientes reducidas, lo que lleva a un dispositivo lento.

La tecnología CMOS mejora estos dos factores:

- Elimina la carga activa. La estructura complementaria hace que solo se consuma corriente en las transiciones, de modo que el transistor de canal P puede aportar la corriente necesaria para cargar rápidamente las capacidades parásitas, con un transistor de canal N más pequeño, de modo que la célula resulta más pequeña que su contrapartida en NMOS.

- En CMOS se suelen sustituir los registros dinámicos por estáticos, debido a que así se puede bajar el reloj hasta cero y las reducidas dimensiones y bajo consumo de la celda CMOS ya no hacen tan atractivos los registros dinámicos.

Por último, se suelen emplear transistores pequeños, poniendo una celda mayor para la interfaz con las patillas, ya que las necesidades de corriente son mucho mayores en las líneas de salida del chip.

La disminución del tamaño de los transistores y otras mejoras condujo a nuevas familias CMOS: AC, ACT, ACQ, etc.

CMOS analógicos

[editar]Los transistores MOS también se emplean en circuitos analógicos, debido a dos características importantes, a saber.

Alta impedancia de entrada

[editar]La puerta de un transistor MOS viene a ser un pequeño condensador, por lo que no existe corriente de polarización. Un transistor, para que pueda funcionar, necesita tensión de polarización.

Baja resistencia de canal

[editar]Un MOS saturado se comporta como una resistencia cuyo valor depende de la superficie del transistor. Es decir, que si se le piden corrientes reducidas, la caída de tensión en el transistor llega a ser muy reducida.

Estas características posibilitan la fabricación de amplificadores operacionales "Rail-to-Rail", en los que el margen de la tensión de salida abarca desde la alimentación negativa a la positiva. También es útil en el diseño de reguladores de tensión lineales y fuentes conmutadas.

CMOS y bipolar

[editar]Se emplean circuitos mixtos bipolar y CMOS tanto en circuitos analógicos como digitales, en un intento de aprovechar lo mejor de ambas tecnologías. En el ámbito analógico destaca la tecnología BiCMOS, que permite mantener la velocidad y precisión de los circuitos bipolares, pero con la alta impedancia de entrada y márgenes de tensión CMOS. En cuanto a las familias digitales, la idea es cortar las líneas de corriente entre alimentación y masa de un circuito bipolar, colocando transistores MOS. Esto debido a que un transistor bipolar se controla por corriente, mientras que uno MOS, por tensión.

La relevancia de estos inconvenientes es muy baja en el diseño microelectrónico actual.

Ventajas e inconvenientes del CMOS

[editar]- Ventajas

La familia lógica tiene una serie de ventajas que la hacen superior a otras en la fabricación de circuitos integrados digitales:

- El bajo consumo de potencia estática, gracias a la alta impedancia de entrada de los transistores de tipo MOSFET y a que, en estado de reposo, un circuito CMOS solo experimentará corrientes parásitas. Esto se debe a que en ninguno de los dos estados lógicos existe un camino directo entre la fuente de alimentación y el terminal de tierra, o lo que es lo mismo, uno de los dos transistores que forman el inversor CMOS básico se encuentra en la región de corte en estado estacionario.

- Gracias a su carácter regenerativo, los circuitos CMOS son robustos frente a ruido o degradación de señal debido a la impedancia del metal de interconexión.

- Los circuitos CMOS son sencillos de diseñar.

- La tecnología de fabricación está muy desarrollada, y es posible conseguir densidades de integración muy altas a un precio mucho menor que otras tecnologías.

- Inconvenientes

Algunos de los inconvenientes son los siguientes:

- Debido al carácter capacitivo de los transistores MOSFET, y al hecho de que estos son empleados por duplicado en parejas nMOS-pMOS, la velocidad de los circuitos CMOS es comparativamente menor que la de otras familias lógicas.

- Son vulnerables a latch-up: Consiste en la existencia de un tiristor parásito en la estructura CMOS que entra en conducción cuando la salida supera la alimentación. Esto se produce con relativa facilidad debido a la componente inductiva de la red de alimentación de los circuitos integrados. El latch-up produce un camino de baja resistencia a la corriente de alimentación que acarrea la destrucción del dispositivo. Siguiendo las técnicas de diseño adecuadas este riesgo es prácticamente nulo. Generalmente es suficiente con espaciar contactos de sustrato y pozos de difusión con suficiente regularidad, para asegurarse de que está sólidamente conectado a masa o alimentación.

- Según se va reduciendo el tamaño de los transistores, las corrientes parásitas empiezan a ser comparables a las corrientes dinámicas (debidas a la conmutación de los dispositivos).

Problemas

[editar]Hay tres problemas principales relacionados con la tecnología CMOS, aunque no son exclusivos de ella.

Sensibilidad a las cargas estáticas

[editar]Históricamente, este problema se ha resuelto mediante protecciones en las entradas del circuito. Pueden ser diodos en inversa conectados a masa y a la alimentación, que, además de proteger el dispositivo, reducen los transitorios o zener conectados a masa. Este último método permite quitar la alimentación de un solo dispositivo.

Latch-up

[editar]Consiste en la existencia de un tiristor parásito en la estructura cmos que se dispara cuando la salida supera la alimentación. Esto se produce con relativa facilidad cuando existen transitorios por usar líneas largas mal adaptadas, excesiva impedancia en la alimentación o alimentación mal desacoplada. El Latch-Up produce un camino de baja resistencia a la corriente de alimentación, de modo que, si no se ha previsto, acarrea la destrucción del dispositivo. Las últimas tecnologías se anuncian como inmunes al latch-up.

Resistencia a la radiación

[editar]El comportamiento de la estructura MOS es sumamente sensible a la existencia de cargas atrapadas en el óxido. Una partícula alfa o beta que atraviese un chip CMOS puede dejar cargas a su paso, cambiando la tensión umbral de los transistores y deteriorando o inutilizando el dispositivo. Por ello existen circuitos "endurecidos" (Hardened), fabricados habitualmente en silicio sobre aislante (SOI).

Referencias

[editar]- ↑ «LA TECNOLOGÍA CMOS». Consultado el 7 de junio de 2019.

- ↑ F. M. Wanlass; C.T. Sah (febrero de 1963). "Nanowatt Logic Using Field-Effect Metal. Oxide Semiconductor Triodes", Solid-State Circuits Conference. Digest of Technical Papers. 1963 IEEE International (en inglés) VI. pp. 32 y 33.

Véase también

[editar]Enlaces externos

[editar] Wikimedia Commons alberga una categoría multimedia sobre CMOS.

Wikimedia Commons alberga una categoría multimedia sobre CMOS.- Usando integrados CMOS